Ϊ��չ��ҵ�ٿ���������Ĺ��ò������ӿڲ������������һ�ָ���AT91RlM9200�ٿ��������ܻ������߲��ģ�����滮�취�Լ���ϵ�Ĺ����ܹ������������ֽӿڵ�����Ӳ�������ƻ�����ģ��ʹ��Ƕ��ʽ��ϵ���������ֽӿ�������ѵ����⣬���нϺõ�ʵ��ʹ��ǰ����

����

MultiBus�DCPUģ���Ǹ���AT91RM9200�ٿ��������ܻ������߲��ģ�顣��CPUģ����Ҫ��ɶ���λ���IJٿأ�����������Modbus�DRTU����Э�������ͨѶ��ϵ�ṹ������ϵ�豸�ܹ���������Modbus�DRTU��ʽ��������ϵ���ο���ʵʱ����ȷ����ɹ�ҵ�ֳ������ռ����ź�����ȹ��ã�һ�𣬹����淶��Ƶ�ӿ���������16λɫͼ�����淶��Ƶ��������ӿ��������¼�������á���ģ����ΪǶ��ʽ�������������ģ�������˻�����Ľ������������֡��������ݵĴ洢���മ�ڡ���USB�ڡ���Ƶ�ź������������̫���ڵȽӿڣ���תLinux������ϵ���ܹ����ٽ�������ʹ�õ�Ƕ��ʽʹ����ϵ��

1 MultiBus�DCPUģ�������滮�ƻ�

Ϊ������ʵ��ʹ�ö�ʵʱ�Ե�Ҫ��MultiBus�DCPUģ������ѡ����Linux2��6��21������ϵ����䣬Linux2��6���ں�ʹ���ܹ�����ռ����һ����ʹ��Linux2��6�ں�������ʵʱ��ϵ��Ƕ��ʽ��ϵ�С�����������Linux�����½��п�����ʹ�ò�ѡ�ù淶��ͨѶЭ��D�DModbusЭ�飬�ٿ��豸�ܹ����ɹ�ҵ������лἯ��ء�������ͬ��Modbus�ӿڣ�MultiBus�DCPUģ������չ��λ��������Ϊ�Ե��豸�ڹ�ҵ�����н��жԻ���ʹ�ø����豸����뵽��ҵ�ٿ������С�MultiBus�DCPUģ��֧���ֽι�ҵ�����ϵ����õ���̫��(UDP)ͨѶ��RS485ͨѶЭ�顣�������ģ��������������ģ�����ͨѶʱ��ѡ��Modbus�DRTU����ͨѶ������ʹ����̫��(UDP)��RS485���߽������ݵķ�������ɣ���ɶԸ�����ģ��ĻἯ��ء���������ṹ��ͼl��ʾ��

2 MulitiBus�DCPUģ��Ӳ���滮�ƻ�

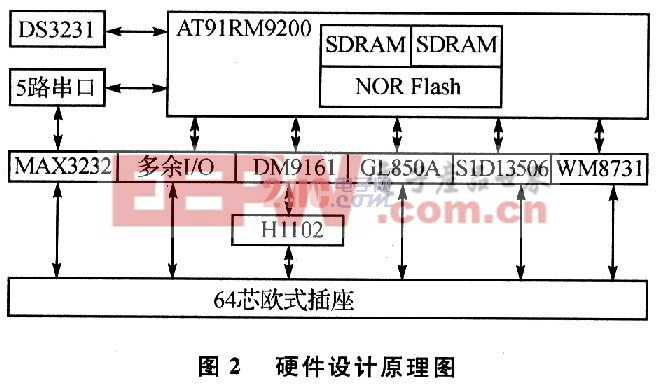

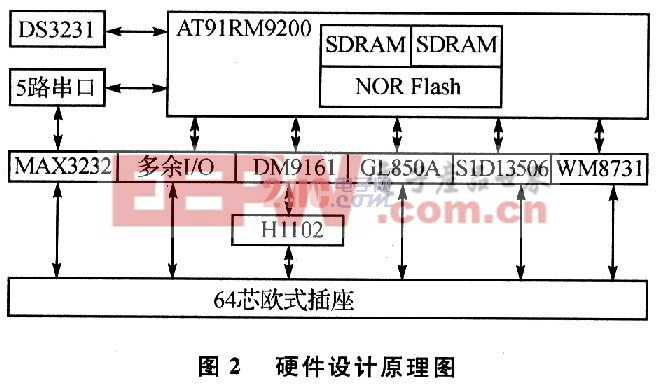

Ӳ���滮ԭ��ͼ��ͼ2��ʾ��MultiBus�DCPUģ��ѡ��Atmel��˾��AT91RM9200Ϊ����������������ARM920T ARM Thumb������������ҵ��180 MHzʱ���øߴ�200 MIPS�����д洢��������Ԫ���ܹ���תLinux��ʵʱ������ϵ������10��100 Base�DT����̫�����ӿڣ�ֻ������һ��PHY���������̫��ͨѶ������USB 2��Oȫ��(12 Mb��s)����˫�˿ڣ��ܹ���չ���̡���ꡢU�̵ȹ淶���衣

��������AT91RM9200����5�����ڣ�1��DEBUG���ڣ��滮ΪRS232�ӿڣ��ܹ�ֱ���ν�PC�Ĵ��ڽ��е��ԣ�1��RS485�ӿڣ��ܹ�����������ģ���RS485�ӿ�������磻����3�����ھ��滮ΪRS232�ӿڡ�

����CPUģ����ⲿ���ߺ�Epson��˾��S1D13506����оƬ��չ��һ��VGA�ӿڣ��ֱ���Ϊ640��480��256ɫ��IS41LVl6100Ϊ�乩�������Դ棬����Ϊ1M��16λ��֧��EDO PAGE��ʽ��

GL850AоƬ��һ�����ĵ�USB 2��0 HUB�ٿ�����AT91RM9200������USB HOST�ӿھ���GL850AоƬ��չΪ4��USB HOST�ӿڡ�

DS3231�Ǿ���ʮ�ָߵ�I2C����ʵʱʱ�ӡ��侫����0��40���ڸߴ��2 ppm����-40��85���ھ��ȿɴ��3��5ppm�����ص�أ�������ܹ����ʱ�̣���Ϊ��ϵ�����롢�֡�Сʱ���ա����ڡ��¡������Ϣ��������������������á�

WM8731��һ������������Ƶ�������(CO-DEC)������������ʷŴ����Ϳɱ�̲��������趨���á�WM8731оƬ����I2S�ӿ���CPU�νӣ�ΪCPUģ����չ����Ƶ�źŵ���������ӿڣ�ʹ��ϵ������Ƶ�������ã���Ƶ�ź����ֻ����ܹ�������̫�����͡�

DM9161Ϊ10��100M������̫�������㵥оƬ�շ�����H1102Ϊ���������ѹ�����������10��100M����Ӧ���ο����紫�书�á�

MultiBus�DCPUģ�龭���������ֲٿ�оƬ����������������ֽӿڣ���ϵ��ת��Ϣ�ܹ�ֱ�Ӿ���VGA���������ֳ��������������˻������Ŀɲ����ԡ�

3 ����ģ��Ӳ���滮�ƻ�

3��1 �ӿ�оƬ��ѡ

�ӿ�оƬѡ��Epson��˾�����Ĵ��ģ���ֲٿ���S1D13506��������SEDl354�ٿ���Ϊ����չ�����ľ��и���õ�LCD���ֲٿ�����֧��ȫ���͡����ģ��LCD��CRT��TV��������S1D13506����RAMDAC(Random Access Memory Digital-to-Analog Converter�������ģ�任������)Ӳ��X-Y��ת�ö�ά������������114���Ĵ������ܹ����������ø��ֲ�ͬ�����ַ�����

3��2 �ӿ�Ӳ���滮

S1D13506�봦�����Ľӿ�ѡ��ͨ����������(�����������ߡ���ַ���ߡ��ٿ�����)���ӿڽ�˵���1���С�оƬ��������ʱ��CLKl��CLK2����ͬ���źŷ�����ICSl523�������ģ����1M��16λ��EDO-DRAM IS41LVl6100��

![]() �����������

�����������